## J-PARC Linac Low Level RF Control

S. Anami<sup>A)</sup>, E. Kadokura<sup>A)</sup>, S. Michizono<sup>A)</sup>, S. Yamaguchi<sup>A)</sup>, E. Chishiro<sup>B)</sup>, T. Kobayashi<sup>B)</sup>, H. Suzuki<sup>B)</sup>

A) KEK, 1-1 Oho, Tsukuba, Ibaraki, 305-0801

B) JAERI, 2-4 Shirakata-Shirane, Tokai, Naka, Ibaraki, 319-1195

#### Abstract

Low-level RF (LLRF) systems for J-PARC Linac generate RF and clock signals, drive klystrons, and stabilize accelerating fields in cavities. The LLRF system is controlled by a programmable logic controller (PLC). PLC control functions are ON/OFF operation interlocked with a protection system, parameter setting for accelerating voltage and feedback PID, and monitor of status and analog data. The PLC is communicated through Ethernet with a touch panel for local operation and with a VME/OPI for remote operation. We describe the LLRF system control using the PLC.

# J-PARCリニアック低電力高周波システムの制御

## 1. はじめに

J-PARC 181-MeV 陽子リニアックの高周波源は、20 台のクライストロン増幅器と 4 台の固体増幅器で構成され、それぞれの高周波制御システムによって空洞加速電圧の振幅及び位相を $\pm 1\%$ 、 $\pm 1^\circ$  の精度に安定化されている。高周波源の安定化の要となるのはフィードバック (FB) 制御部であり、なるの努力の多くが注がれている[1]。しかし、システムの制御と言う観点から見るならば、この FB 制御当いるり、全ての構成機器を統括的に制御していると言える。この PLC では、操作・設定・監視などと共に自動復帰や自動コンディショニングと言った機能も備えていなければならない。

## 2. 低電力高周波システムの構成

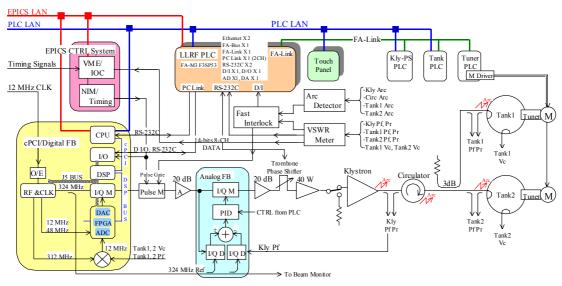

低電力高周波システムは、それぞれのクライスト ロン(及び固体増幅器)に対応し、図1に示すよう な構成となっている。その高周波制御としての基本 機能は、先ず、リニアック最上流部から送られてく る 12MHz の光基準信号を元に加速周波数信号 (324MHz) 及びディジタル FB に必要となる各種 周波数信号(12MHz、48MHz、312MHz)を発生さ せ<sup>[2]</sup>、ディジタル FB 回路の PID (比例・積分・微分、 但し微分は使用してない) コントローラによって振 幅·位相を制御し、その RF 信号を 40W アンプで増 幅して、2.5MW クライストロンを励振している。 このシステムには、空洞を含む全体ループの ディジタル FB の他に、40W アンプ及びクライスト ロンからなるローカルなアナログ FB がある。この アナログ FB は、クライストロン増幅器を線形なも のとするためのもので、その帯域幅を外ループの ディジタル FB に比べ十分広いものにし、お互いが 干渉しないようにしている。

図1 低電力高周波システムの構成ブロック図

## 3. 低電力高周波システムの制御構成

低電力高周波システムを制御機能の観点から図 1 を見ると、制御の中心に PLC があり、全ての構成機器がこの PLC に接続されている。以下にこれら機器の制御的な機能について述べる。

#### 3.1 PLC

図1には示してないが、低電力高周波システム用のPLCには、CPUモジュールを持つ親機とCPUを持たず親機の拡張(FA)バス上に接続される子機とがある。親機は4システムに1台の割合である。図1はPLCが親機の場合を示している。子機と親機との違いは、子機にはPLCのLANへ接続及び他のPLCとのリンクがないことの2点であるが、他は全て同様なシステム構成となっている。前節までと同様に、以下は親機PLCを持つシステムについて述べる。

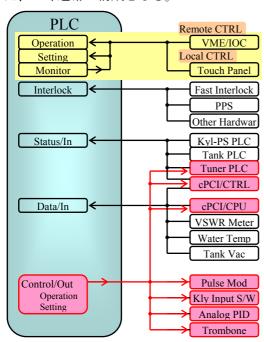

PLCのモジュール構成は図1に示す通りであるが、これを機能面で見ると、図2のように表すことが出来る。先ず、PLCへの操作・設定・監視のアクセスとしては、遠隔用に VME/IOC があり、現場用としてTouch Panel (TP) がある。両者は TP にある切換えSW によりどちらかの一方のみが選択される。各機器からのインターロック、ステータス、アナログデータなどの入力信号は、それぞれ専用のモジュール、或いは通信モジュールから PLC へ取り込まれ、ラダープログラム上のステートマシンを遷移させる。これらの結果として制御出力があり、実際の動作を各機器へ与える事になる。この様に PLC への入出力媒体を無視して、機能面だけで見ると、実に整然とした、ごく通常の構成となる。

図2 PLCの機能接続図

#### 3.2 Touch Panel (TP)

TP は現場用 GUI を提供するものであり、ON/OFF やパラメータ設定、各種の監視など、制御に必要な全ての機能を備えている。また、加速電圧の振幅や位相、空洞の真空度など重要なデータは、トレンドグラフに表示され、それぞれの安定度を時間的な推移で視覚的に捉えることが出来る。

#### 3.3 EPICS VME/IOC

VME/IOC は Linac 全体制御が提供する EPICS 系への I/O インターフェースであり、EPICS LAN 上にある EPICS/OPI によって PLC が遠隔操作される。本来は VME ボードに直接機器を接続する形態であるが、Ethernet モジュールを経由した PLC レジスタへの Read/Write によって制御される。本システムで唯一 I/O に直接接続されているのは更新頻度の高い VSWR Meter からの 8CH データのみである(図 1)。

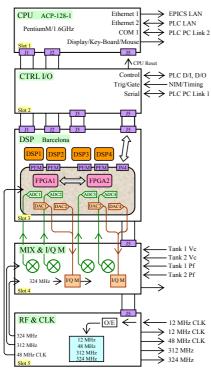

#### 3.4 Compact PCI System

ディジタル FB を担う cPCI システムのモジュール別構成を図 3 に示す。本来の cPCI システムバス J1、J2 を使用しているのは CPU 及び DSP ボードのみであり、他のモジュールは、J3 と J5 をユーザバスとして使用しているが、単に cPCI 規格の箱を利用しているのに過ぎない。

使用する CPU ボードは、PentiumM/1.6GHz を搭載したアバールデータ社の ACP-128-1 を予定している。2 幅の前面パネルには、ここで用いる 2 つの Ethernet ポートや Com ポートの他、各種入出力デバイスポートが装備されており、現場でのデバッグやモニタを容易なものにしている。

DSP ボードには、TMS320C6701 を 4 個搭載した Spectrum Signal 社の Barcelona を採用している。このボードは、夫々の DSP 外部メモリバスに直通した PEM と呼ばれる I/O インターフェースを持ち、装着されるメザニンカードとの間で高速データ転送(400BM/s)を可能にしている。J1、J2 とは別に、J3 には各 DSP のシリアルポート及び割り込みラインを当て、J5 にはユーザバスとしてメザニンカード用コネクタ(JN4)へ通じる経路を与えている。

この DSP ボードのメザニンカードとなるカスタム FPGA ボードには、Xilinx 社の XCV600E(FG 676)を 2 個、ADC、DAC それぞれ 4 個を搭載し、全ての PEM ポート(60 ピンコネクタ×8)と JN4とを配線し、出来るだけ拡張性の高いものとしている。この FPGA ボードは、入力として 4 つの ADCが、出力として 4 つの DACがあり、途中で FPGAが信号処置とプロセス処理をしているとみる事が出来る。4 入出力それぞれの接続は、隣接する MIX & I/Q M との間を同軸ケーブルで直接配線している。尚、FPGAのコンフィギュレーション用 EEPROMの書き換えは、通常の JTAG ポートに加え、CPUホストから PCI バス、DSP、PEM、FPGA を経由して行えるようにもなっている。

Control I/O ボードは、PLC や NIM/Timing から J5 バスへの中継であり、ほとんどの信号は FPGA へ送

図3 cPCIのモジュール構成図

られる。この他、FPGA から Fast Interlock への OK 信号の伝達もある。また、J3 を経由した DSP と PLC とのシリアル通信の経路も中継している。この通信は、FPGA に読み込まれた空洞の位相情報を元に DSP が同調ずれを算出し、空洞を自動的に同調させるための専用回線である。

以上は何れも CPU ホストを経由しない制御回線についてであるが、以下の 3 回線 (COM 及び Ethernet 2 回戦) は CPU 上の OS (Linux) のサービスによる通信である。この内 COM ポートは、フィードバックシステムとして必要な全信号(操作・設定・監視)を PLC との間で交信する重要なものである。ただ、波形の監視データについては、そのデータ量から COM ポートから PLC への転送と言う訳に行かず、Ethernet による EPICS への送り出しとなっている。但し、OS に EPICS を組み込んで CA (Channel Access) サーバとするための開発が未着手であるため、先ずは本システムを FTP サーバとして機能させる予定である。

もう一方の Ethernet ポートは PLC LAN に接続されているが、これは PLC との通信のためではなく、この LAN 上にある cPCI 用 PC サーバとの通信のためである。このサーバによって、OS のネットワークブート、DSP の実行ファイルや FPGA のコンフィグレーションファイルのダウンロードなど、システムの立ち上がりから定常動作に至るまでに必要な全環境が提供される。

#### 3.5 Fast Interlock、Arc Detector及びVSWR Meter

クライストロン出力の大電力高周波が放電や異常 反射した場合、高周波窓やサーキュレータを保護す るために、高速に高周波を遮断する必要がある。 PLC を経由したのでは余りにも遅くなるため、検出器(Arc Detector 及び VSWR Meter)からの信号で直接ハードウェアにインターロックを掛ける Fast Interlock 回路を設けている。この回路の論理和出力によって、Pulse Modulator のゲートを閉じ、クライストロン出力の RF を  $1\mu$ s 以下の高速で遮断する。

Arc Detector の入力は 4 回路 (クライストロン窓、サーキュレータ、及びタンク 1、2 の入力窓) あり、夫々光ファイバーによって送られてくるアーク信号を光で受けている。この様に直接光入力としているのは、高速応答時のノイズ誤動作を避ける為である。

VSWR メータは、入力として進行波(Pf)及び反 射波(Pr)のペアが 3 回路(クライストロン出力及 びタンク 1、2 の入力) あり、その値はこれら入力 の検波波形をディジタイズし、論理素子や FPGA で 演算した値である。このため 5μs 程度の遅れは避 け難く、場合によっては致命的な遅れにもなりうる。 そのため、反射波電力の大きさをアナログでコンパ レートし、その過大反射電力でも動作するようにし ている。また、この VSWR メータはパワーメータ の機能も備え、先の Pf、Pr に加えタンク 1、2 の空 洞電圧(Vc)も計測している。この計測値は、 2MHz サンプルの 32 点平均を FPGA で算出した 12 ビット長の値である。最大50 Hzの繰り返しでも取 りこぼしなくデータを残すために、VME/IOC の 128 ビットディジタル入力モジュールヘデータを 送っている。一方、PLC へは 5 Hz 程度に間引かれ た値が、シリアル通信で送られる。

Fast Interlock では、放電時のアークや VSWR からの入力の他、外部からの高速 RF 遮断 (MPS からの「RF OUT Enable」信号)などの入力も備えている。これらは何れも RF を高速に遮断する Fast Interlock そのものの機能であるが、この他に高周波源の正常を外部 (MPS) へ高速に知らせる「RF ACC OK」信号の出力機能も有している。この信号は、全ての高周波源機器が正常に動作し、ビーム加速に対してレディ状態である事を意味し、Fast Interlock からの出力の他、cPCI での FB が正常、タンク 1、2 の空洞電圧が正常値にあるなどの条件も加わっている。

## 4. 現在の状況

低電力高周波システムは、2 台の試作機が 60 MeV リニアックで DTL-1 とテストベンチのステーション で使用されており、実機用の全数は平成 17 年春の 納入、据付予定である。現稼動中の PLC プログラム は全面的に書き換える予定で、開発を進めている。

#### 参考文献

- [1] S. Michizono, et al., "Digital RF Control System for 400-MeV Proton Linac of JAERI/KEK Joint Project", Proc of Linear Accelerator Conference 2002, 2002

- [2] T. Kobayashi, et al., "RF and Timing Reference Distribution System for J-PARC Linae", in this meeting